Method of inputing and outputing data in NAND flash using software(S/W) error correction code(ECC) and embedded system using the same method

KR100949471B1 - 소프트웨어(s/w) 에러정정코드(ecc)를 이용한낸드 플래시에서의 데이터

제1 항에 있어서, 상기 낸드 플래시의 한 블럭 내의 최초 페이지 쓰기의 경우에는 상기 S/W ECC는 상기 최초 페이지의 쓰기 명령 이전에 동작하는 것을 특징으로 하는 낸드 플래시에서의 데이터 입

patents.google.com

- NAND Flash Memory?

- 블록 단위로 구성, 블록은 페이지 단위로 구성, 한 페이지는 데이터 영역과 스페어 영역으로 구분

- 데이터 영역 : 데이터가 저장

- 스페어 영역 : 데이터의 오류정정부호(parity)가 저장

- 페이지 단위로 읽기 동작 수행, 블록 단위로 쓰기 동작 수행

→ 이유 : 낸드 플래시 메모리에서 데이터를 저장하기 위해서는 데이터 저장 위치의 데이터를 지우는 작업이 우선되어야 함. 지우는 작업의 단위가 블록 단위로 이루어지므로 쓰기 또한 블록 단위로 수행

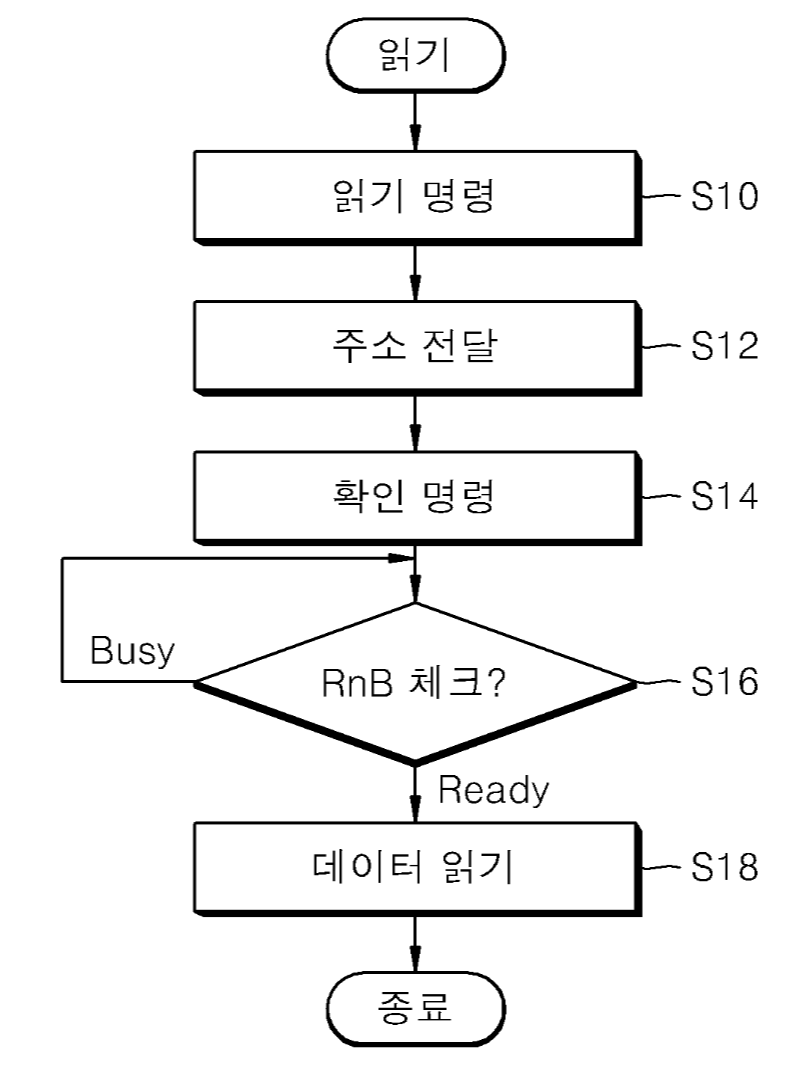

- NAND Flash에서 읽기 수행 과정

- 읽기

- S10 : 낸드 플래시 인터페이스를 통해 읽기 명령 전송

- S12 : 해당 주소 전달

- S14 : 확인 명령 전송

- S16 : RnB(Ready or Busy) 체크 수행

- S18 : Ready일 시 페이지에서 데이터를 읽음

- 종료

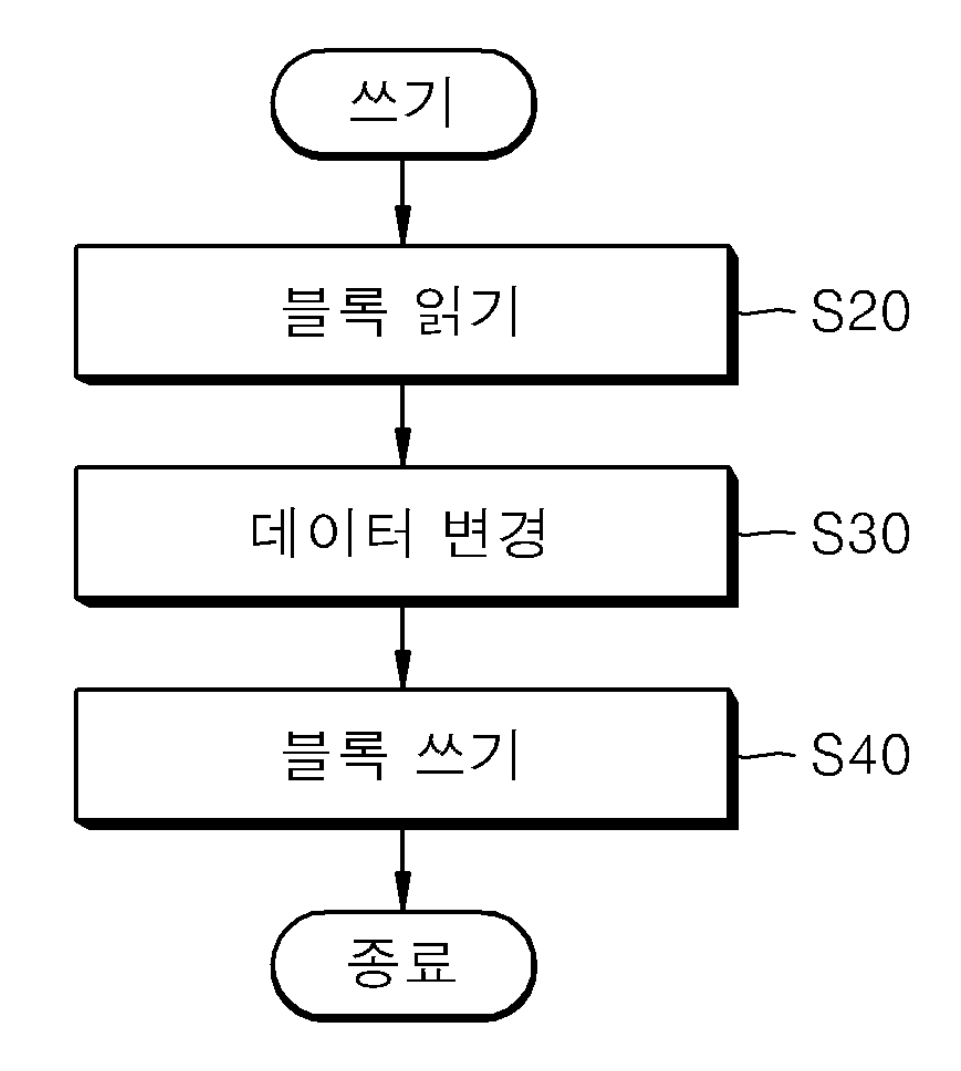

- NAND Flash에서 쓰기 수행 과정

- 쓰기

- S20 : 낸드 플레시 인터페이스를 통해 블록 읽기

- S30 : 데이터 변경(해당 블록에서 데이터 삭제)

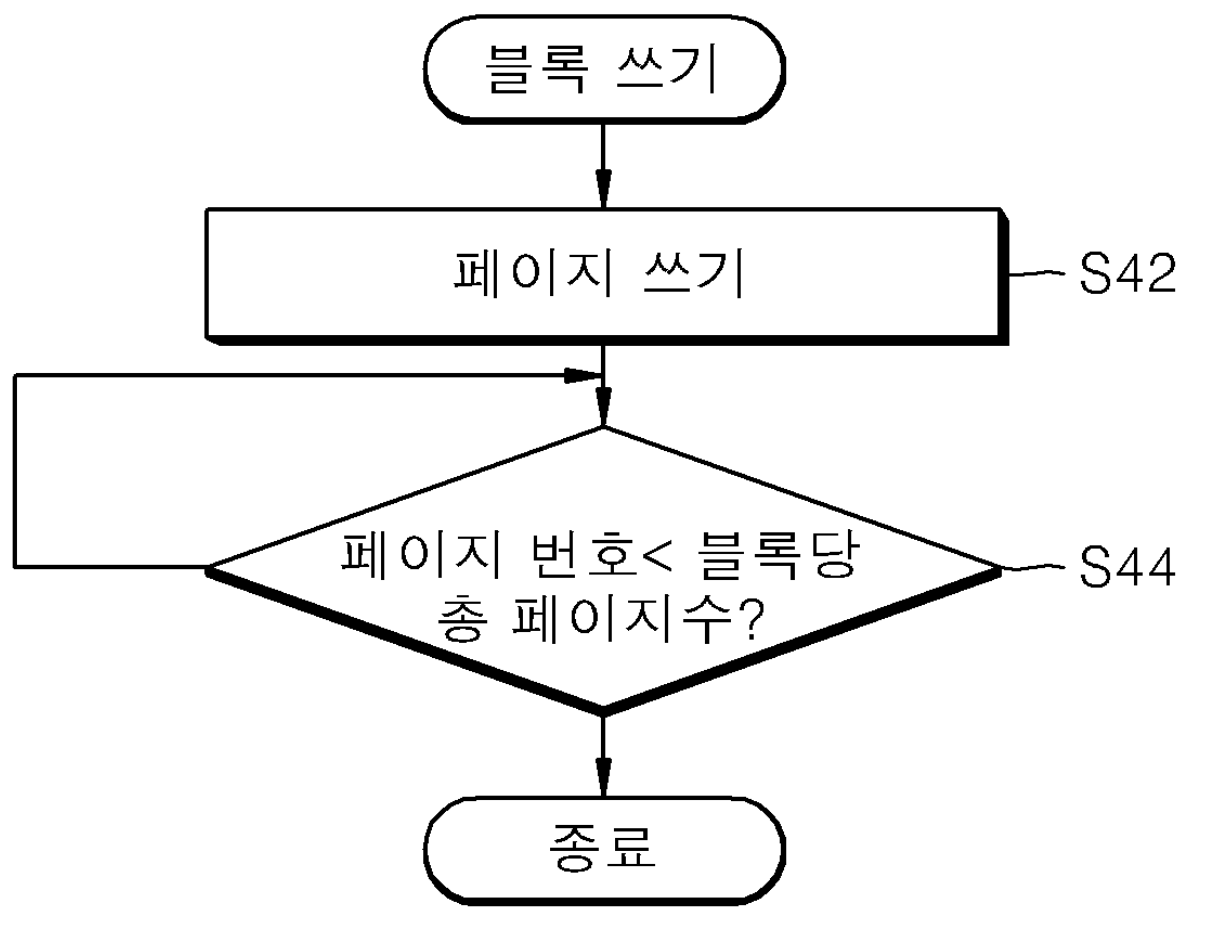

- S40 : 블록 쓰기

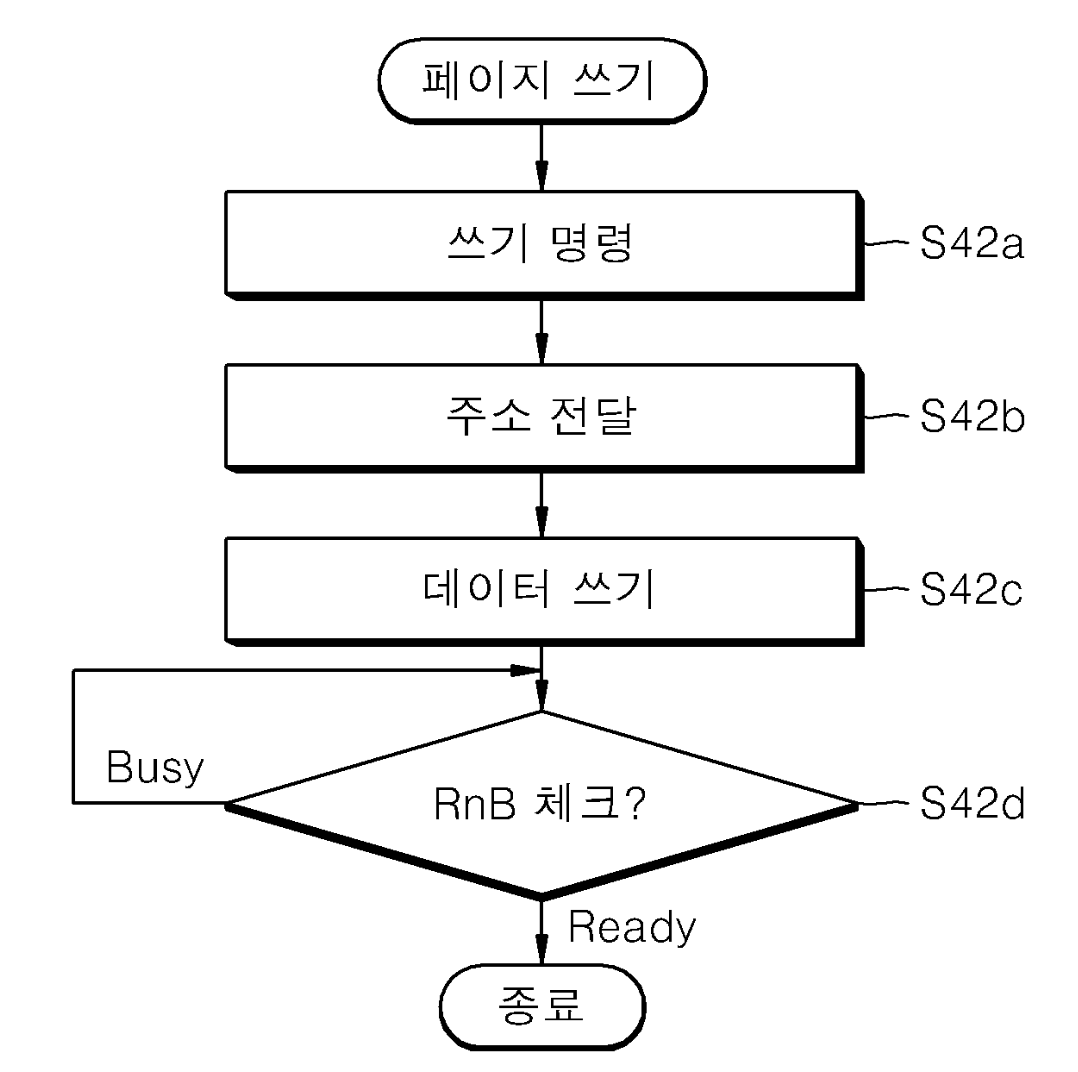

- S42 : 순차적으로 페이지에 데이터 쓰기

- S42a : 쓰기 명령 전달

- S42b : 주소 전달

- S42c : 데이터 쓰기

- S42d : RnB 체크로 페이지에 대한 데이터 쓰기가 완료됐는지 검사

- S44: 블록 당 총 페이지 수와 동일한지 비교

- S42 : 순차적으로 페이지에 데이터 쓰기

- 종료

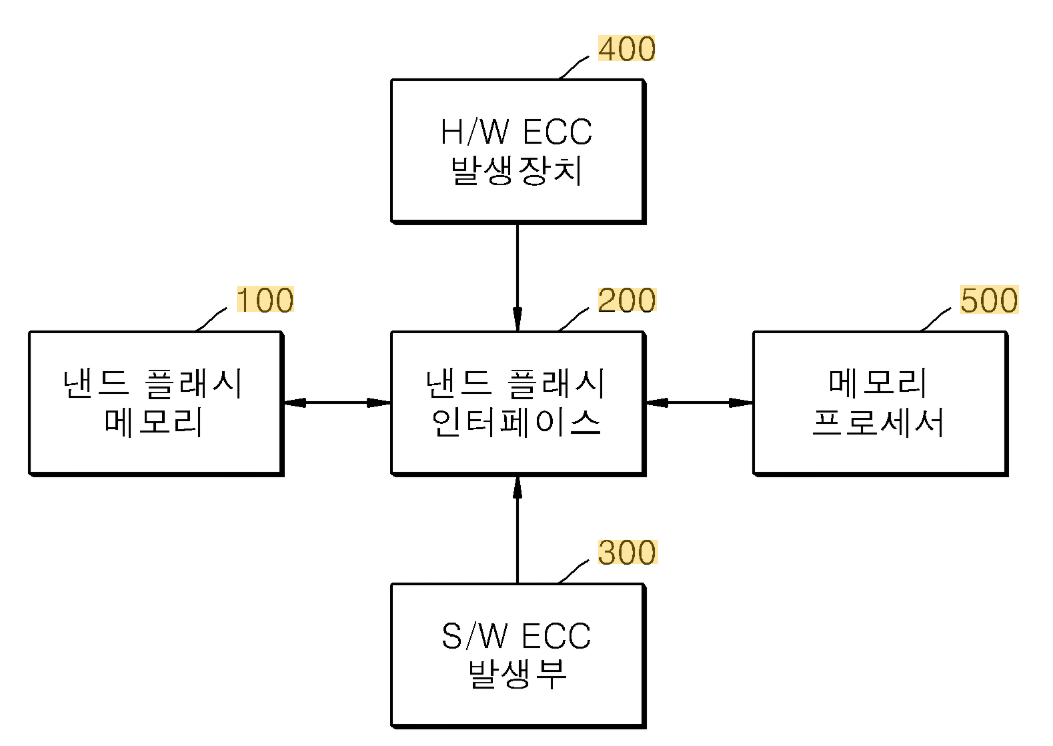

- H/W 에러 정정 코드(Error Correction Code: ECC)

읽기 또는 쓰기 동작 중 발생하는 오류를 검사 및 정정하기 위하여 낸드 플레시 인터페이스에 동기화되어 있는 HW ECC를 이용 - 오류정정부호(parity)를 발생시켜 오류 정정

H/W ECC의 한계

- 고정적 오류 정정법이라 MLC 등 다양한 구조에 대응하기 어려움

- 칩을 리비전하거나 교체해야 하는 번거로움

So, S/W ECC의 도입

- S/W ECC와 H/W ECC의 역할 분담

- H/W ECC : 실시간으로 스페어 영역 패리티를 생성·검증 → 추가 시간 거의 없음.

페이지 스페어 영역에 붙는 즉시 ECC 생성해 전송 - S/W ECC : 블록/페이지 단위 데이터 전체에 대해 오류 정정 가능 → MLC 구조 등에서 발생하는 한계를 보완.

- S/W ECC를 포함한 읽기와 쓰기 동작

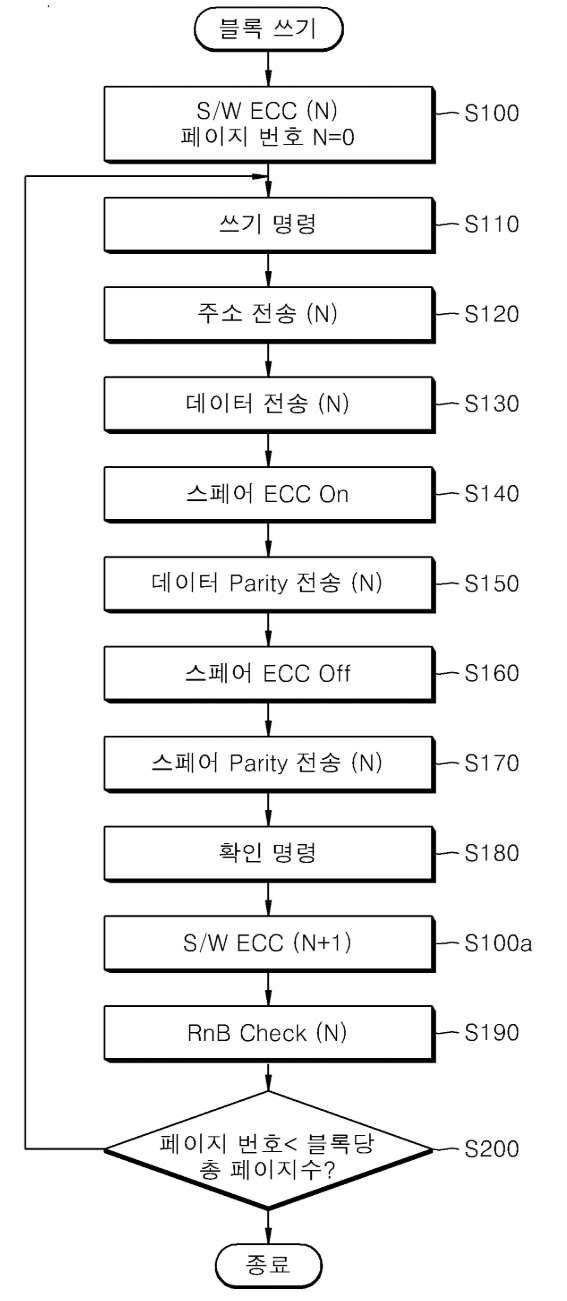

1. 쓰기 동작

- 현재 페이지 쓰기가 끝난 직후가 아니라, 블록 단위에서 다음 페이지를 위해 미리 ECC를 계산함

(블록의 첫 페이지는 예외) - 한 블록 안에서 페이지를 순서대로 쓰면서

[쓰기 → RnB check → 다음 페이지 ECC 미리 생성 → 다시 쓰기]를 마지막 페이지까지 반복. - 쓰기는 페이지 단위가 아니라 블록 단위로 이루어지므로 다음 페이지용 계산이 가능

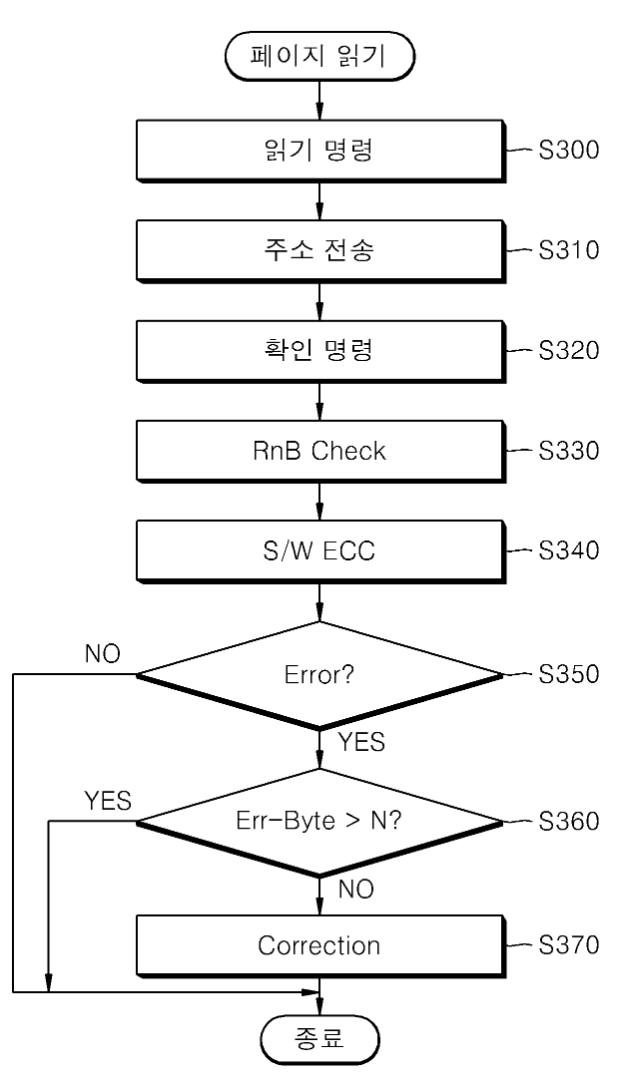

2. 읽기 동작

[명령 전송 → 주소 전송 → 확인 → RnB 체크 → S/W ECC 동작으로 데이터 읽기 오류 검출 및 수정]

- 페이지 단위이므로 RnB 대기 시간이 없음 → 최적의 위치가 없음

→ 읽기 끝난 후 S/W ECC 루틴 추가해 오류 정정 처리 - S/W ECC가 에러 위치가 수정 가능한 범위(바이트 단위)인지 확인.

- 가능하면 수정, 불가능하면 그대로 에러 처리.

- 제약 : ECC 정정 가능 바이트 수(N바이트 한계)를 초과하면 수정 불가

- S/W ECC의 장점

- 속도 면에서 H/W ECC와 거의 비슷해 실사용에 무리 없음

- ECC 연산에 대한 대기 시간 숨기기

: 쓰기 동작 중 가장 오래 걸리는 RnB 대기 구간을 활용해 다음 페이지용 S/W ECC를 수행

→ 시스템 성능 저하를 최소화. - H/W ECC만으로는 MLC 구조에서의 높은 오류율을 처리하기 어려움

→ S/W ECC를 추가로 활용하여 칩 리비전이나 교체 없이 다양한 낸드 구조(Mono/MLC 등)에 대응 가능 - 펌웨어/소프트웨어 레벨에서 구현 가능하므로 하드웨어 설계 변경 없이 간단히 시스템에 적용 가능

→ 임베디드 시스템에서 비용, 호환성 측면에서 유리.

이후...

ECC 개념 공부를 하려고 낚아올린 doc인데...

세미나 때 피드백으로 들은 충격적인 소식들.

충격적인 소식1 : 현재 ECC는 HW로 하고 있다...

충격적인 소식2 : 특허 문서는 굳이 읽지 않는 게...

진짜 극악의 가독성 문서를 오기로 끝까지 읽어 정리했는데 참 슬픈...

목적에 맞는 문서인지 알지 못하는 무지랭이는 어쩔 수 없다.

반응형

'My Laboratory' 카테고리의 다른 글

| [NVMeVirt] Implementation of DFTL : evaluation (0) | 2025.12.26 |

|---|---|

| [NVMeVirt] Implementation of DFTL #3 : write (0) | 2025.09.24 |

| [NVMeVirt] implementation of DFTL #2 : read (1) | 2025.09.10 |

| [NVMeVirt] implementation of DFTL #1 (0) | 2025.09.04 |

| Paper Review : NVMeVirt: A Versatile Software-defined Virtual NVMe Device (0) | 2025.08.08 |